JEST TCS & IISc CSA Research Interview Experience 2024

May 30, 2024

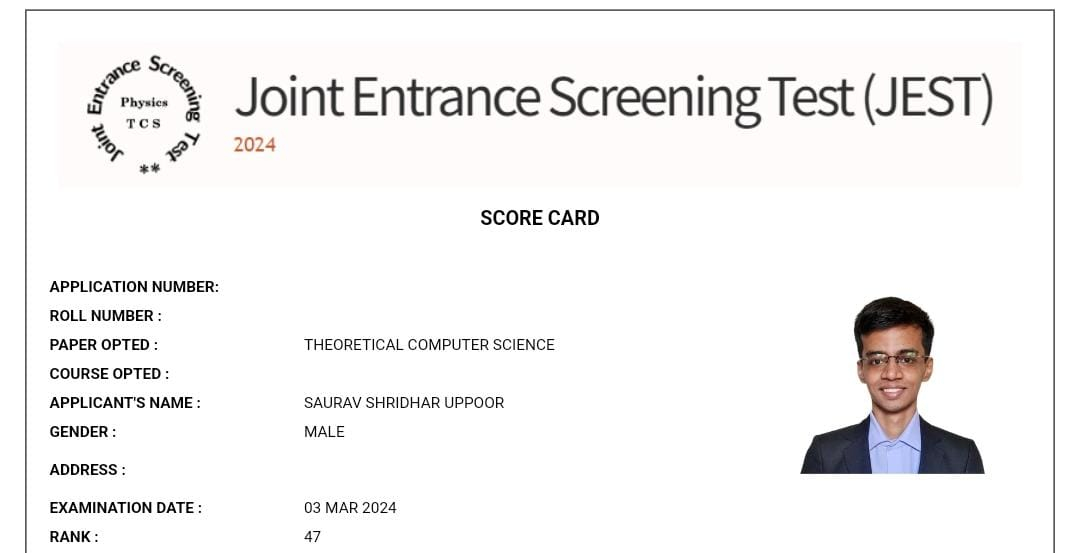

I got a rank of 47 in the JEST Theoretical Computer Science 2024 examination. Result of which, I qualified for research program interviews of various premier institutes and fortunately, received the following offers through these interviews:

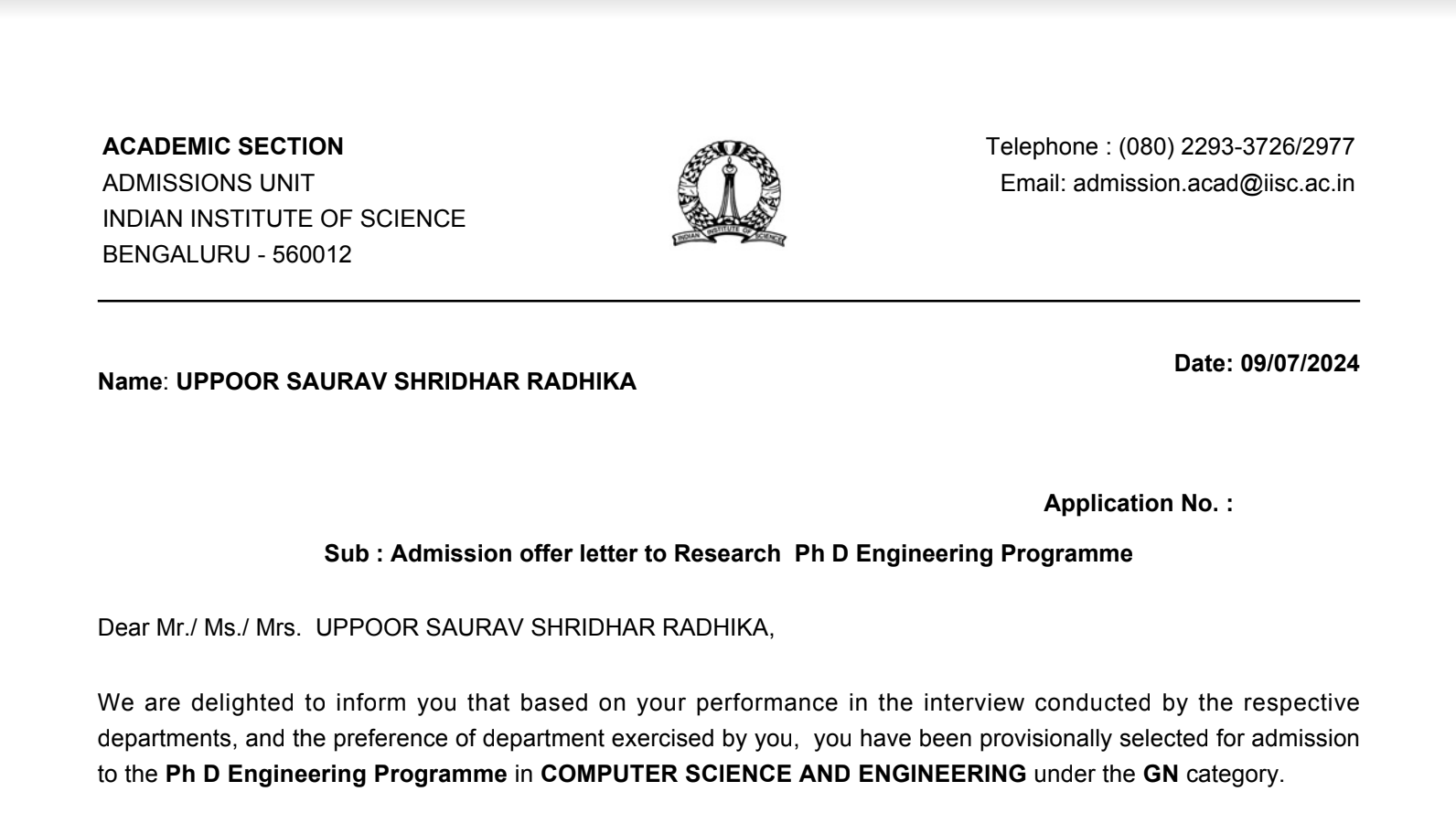

PhD, IISc Bangalore Computer Science & Automation department

MTech RA, IIT Bombay Computer Science Engineering department (via GATE CS)

This post contains my experience with the JEST examination and the research interview process following it.

JEST examination

Joint Entrance Screening Test (JEST) in TCS is a preliminary screening test conducted by various top research institutes in the country. This test consists of problems from following topics:

Analytical Reasoning & Deductions, Combinatorics, Algorithms, Graph Theory, Theory of Computation, Discrete Mathematics & Proofs

The test has two sections - Part A: consists of 25 MCQ problems, 3 marks each for correct response and -1 for incorrect response, Part B: 7 subjective problems for 10 marks each where you are expected to provide proof-based deductions or algorithm with expected time and space complexity.

Ranks are determined solely based on Part A performance. Part B is considered for PhD admissions of IMSc. IISc for their PhD (and Mtech. Research up until 2020) considers just the Part A scores. JEST TCS question papers are never released, however they are similar in difficulty level to the TIFR CS PhD papers.

|

JEST TCS 2024 Scorecard |

Application & Shortlisting Criteria

With my GATE and JEST scores, I applied to the Master's Research programs of IISc CSA and CDS, IIT Bombay and IIT Madras. Considering previous year cutoffs, I was sure of receiving written test/interview calls from both the aforementioned IITs, however couldn't say the same for IISc due to the fluctuating cutoffs depending on the number of applications, vacancies and so on. As expected, I received the test/interview calls from IIT Madras for MS Research and IIT Bombay for MTech RA, MS RA and MS TA. On April 18, I finally received an interview call from IISc CSA department through JEST mode of entry, missed the cutoff for CDS by whisker. Research program cutoffs for 2024 GEN category were as follows:

| Institute | Department | Program | GATE CS Score | JEST TCS Score |

| IISc Bangalore | Computer Science and Automation | MTech Research | 750 | All |

| IISc Bangalore | Computational Data Sciences | MTech Research | 710 | 30 |

| IIT Bombay | Computer Science Engineering | MTech RA/RAP | 650 | - |

| IIT Bombay | Computer Science Engineering | MS RA/RAP/TA/TAP | 600 | - |

| IIT Madras | Computer Science Engineering | MS Research | 600 | - |

For the sake of brevity, I'll restrict this text to only IISc's experience.

Interview Experience

At IISc, the interviews for both MTech Research and PhD candidates happen together. This year it was scheduled across 5 days from May 13 - 17. Mine was scheduled on May 16 at 9 am. Few weeks before the interview, we were asked to select the research pool, 2 research areas within the pool and 2 background subjects (pool selection letter from CSA). CSA contains three pools - Theory, Systems and Intelligent Systems. I chose Systems pool; Computer Architecture, Operating Systems as research area and Data Structures Algorithms, Operating System as background subjects.

On the day, I showed up at the institute at 8.30 am along with 30 other candidates. I was expecting a written test before the interviews (from all the previous year interviews I had read up). However, there were no written tests this year in CSA! We all gathered in a room, where we were asked to fill the pool and research area preferences again (not sure why), following which we were dispersed to different rooms as per our pool. They were courteous to offer us tea/coffee, but I was nervous to have any. Theory pool had 3 candidates, Systems had 6 and rest were all in Intelligent Systems!

We headed to the Chairman's room for our systems interview, I knew Prof. Vinod Ganapathy was the chair this year, so expected him to be in the interview panel. We were waiting outside the room, I was first in line and at exactly 9.30 guess who called me in, Prof. Vinod himself! The interview panel consisted of Arkaprava Basu, Sumit Mandal, R. Govindarajan, K.V. Raghavan and Vinod Ganapathy.

After a brief intro, work experience and motivation for my application, they confirmed the research interests. I had filled Compiler instead of OS initially in the form but had later changed it, the panel didn't seemed to receive the latest revision. I was asked if I wanted to change the research area one last time before the interview, seeing the funny side everyone laughed which lightened the situation somewhat. Then the interview began with basic DSA, I proceeded to the whiteboard:

[Sumit Mandal (SM)] How'd you denote a Node in a Linked List? (used struct)

[SM] Write an algorithm to reverse a singly Linked List. (wrote an iterative code covering all the edge cases)

[Arkaprava Basu (AB)] Write the recursive approach and return the head of the reversed LL. (done)

[AB] Run it through a sample test case and show the Stack memory contents (for some reason they felt I might've missed some initialisation, but following the test case dry run they were convinced all was good).

[AB] Lets move to Operating Systems, I see you have mentioned Codeforces and Codechef in your application (we had to mention achievements and I had added my competitive programming achievements), what do you mean by Segmentation Fault? (answered)

[AB] What kind of address does a CPU core generate? (virtual)

[AB] Explain the entire process of CPU memory request which will result in SegFault. (I explained about the VFN to PFN translation using TLB and page walk, and explained that the page reference will be invalid during this stage and an exception will occur.)

[AB] What happens to the control flow after such an exception? (I tried explaining the process being moved out, but AB wasn't satisfied. He gave few hints about signals which the kernel would generate but I couldn't pick up on the hints.)

[AB] Ok, I'm done with OS, we can move forward to next subject. (I was dejected after this as I was not able to answer the last question.)

It was almost an hour and Prof. Vinod mentioned that we can stop now. But Prof. Govindarajan stated that he has a few questions.

[R. Govindarajan (RG)] Let's move to COA, what do you know about Cache Memory? (explained the flow by completing the TLB/Page walk diagram for TL hit scenario.)

[RG] Can you have Tag bits of Cache in LSB instead of MSB? (I knew we can, so answered yes.)

[RG] What will be the implication of such a change? (I informed the mapping of frames to memory lines will change and there would be interleaving, I tried explaining this with some example on the board, but couldn't complete as they decided to do a hard stop due to time).

The interview went for close to 1h 15m. It was surreal having discussion with those professors who are all top shots in their area of research. They were very polite and provided hints whenever I was stuck. However, I was very dejected that I couldn't answer one of Prof. Arka's question and completely conclude the last question. Nevertheless, I roamed around the lush green campus and clicked a few photos as memory of this day.

|

IISc Main Building; as seen through my phone's camera |

Result

On May 18, CSA released the shortlisted candidates for research program and I was surprised to find my application number listed as well. But this wasn't it, in CSA this is a provisional list and does not guarantee an admission. The final call is with the IISc admission committee who send the offer letters based on the vacancies and hostel availability.

Update: On July 9, I received the PhD offer from IISc Bangalore from the CSA department. To my surpise, I was also informed by the admissions unit that JEST applicants were no longer eligible for the Mtech. Research program in IISc.

I have decided to continue in the industry at this point in time as I believe there's still a lot of avenues to explore.

|

IISc CSA PhD Offer Letter |